Digital Circuits and Systems Design

The digital circuits and systems design group specializes in the analysis, design and optimization of state-of-the-art digital integrated circuits for a broad range of applications such as audio and video codecs, navigation receiver baseband, computer vision and machine learning. The research in the group concentrates on improving energy efficiency of application specific hardware architecture by orders of magnitude, which is the key to enable complex algorithms on power limited platforms.

We take advantages of the parallelism of algorithms and a hardware/software co-design method to map the workloads into heterogeneous systems with customized accelerators, which are complementary to general purpose processors.

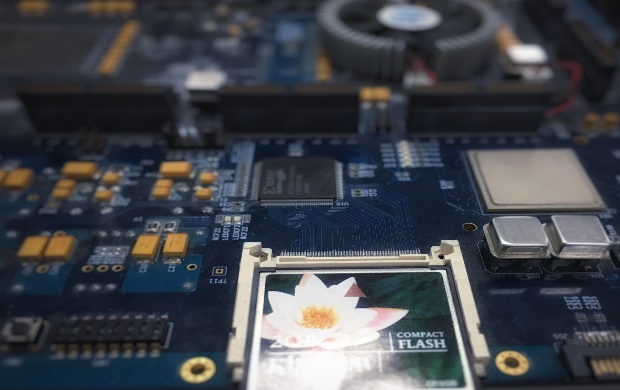

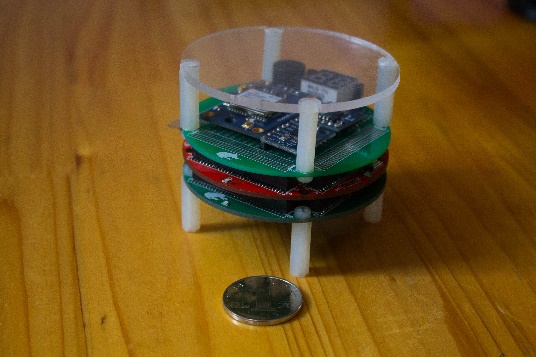

Right now we are developing an intelligent information processing platform for environment sensing and scene understanding. It will be a scalable and flexible system which consists of lightweight RISC scalar cores, high-performance vector engines and efficient hardware accelerators for image processing and deep learning. The parallel multi-core architecture aims to satisfy the requirement of data fusion on modern intelligent devices, where data sources come from multiple sensors such as cameras, microphone arrays, inertial measurement units and ultrasonic ranging units. At the meanwhile, it allows real-time information processing and decision making on a single platform without exceeding the power budget. Besides, the heterogeneous platform will support OpenCL and OpenVX standards in favor of programing and debugging. To embrace the spirit of open source, we plan to release the hardware IPs for image processing and computer vision, which is compatible with OpenVX APIs.

The group has accumulated a wealth of experience in processor, ASIC, SoC design and. We have built a complete EDA environment and developed a series of EDA tools for rapid prototyping. In addition, industrial management and standard design flow are adopted to guarantee the high quality of chips.

Projects

DSP architecture and real-time signal processing technology

- configurable DSP with ISA extension and complier optimization

- network on chip architecture with near threshold computing

- navigation baseband signal processing technology

- low power signal processing technology

multimedia codecs architecture technology

- multiple standards compatible audio codec and its VLSI implementation

- ultra low bit speech encoder and its ASIP implementation

- real-time HD video codec and its VLSI implementation

reliable chip architecture technology

- reliability reinforcement based on many-core arrays architecture

- SoC reliability improvement by hardware/software co-design method

Publications

A 42fps Full-HD ORB Feature Extraction Accelerator with Reduced Memory Overhead

Rongdi Sun, Peilin Liu, Jun Wang, Cecil Accetti, Abid A. Naqvi

2017 International Conference on Field-Programmable Technology

A Low Latency Feature Extraction Accelerator with Reduced Internal Memory

Rongdi Sun, Peilin Liu, Jun Wang, Zunquan Zhou

2017 IEEE International Symposium on Circuits and Systems

HAVA: Heterogeneous Multicore ASIP for Multichannel Low-Bit-Rate Vocoder Applications

Zhenqi Wei, Peilin Liu, Rongdi Sun, Jun Dai, Zunquan Zhou, Xiangming Geng, and Rendong Ying

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Volume 24, Issue 7, July 2016, Pages 2593-2597

HyDMA: Low-Latency Inter-Core DMA Based on A Hybrid Packet-Circuit Switching Network-on-Chip

Zhenqi Wei, Peilin Liu, Rongdi Sun, Zunquan Zhou, Ke Jin, and Dajiang Zhou

IEICE Electronics Express, Volume 13, Issue 14, June 2016, Pages 1-12

HyBar: High Efficient Barrier Synchronization Based On A Hybrid Packet-Circuit Switching Network-on-Chip

Zhenqi Wei, Peilin Liu, and Rongdi Sun

Science China Information Sciences

A Hardware Accelerated Scale Invariant Feature Detector for Realtime Visual Localization and Mapping

Zunquan Zhou, Rendong Ying, Rongdi Sun, Zhenqi Wei, Ke Jin and Peilin Liu

UPINLBS 2016

A flexible processing circuit of morphological transform for obstacle detection

Rongdi Sun, Peilin Liu, Zhenqi Wei

UPINLBS 2016

TAB barrier: Hybrid barrier synchronization for NoC-based processors

Zhenqi Wei, Peilin Liu, Rongdi Sun, and Rendong Ying

2015 IEEE International Symposium on Circuits and Systems

High-efficient queue-based spin locks for Network-on-Chip processors

Zhenqi Wei, Peilin Liu, Rongdi Sun, and Rendong Ying

2014 IEEE Asia Pacific Conference on Circuits and Systems

Instructionbased high-efficient synchronization in a many-core Network-on-Chip processor

Zhenqi Wei, Peilin Liu, Zhencheng Zeng, Jiangwei Xu, and Rendong Ying

2014

IEEE International Symposium on Circuits and Systems

Design of Arithmetic Operation Core in Embedded Processor for High Definition Audio Applications

Zhenqi Wei, Peilin Liu, Ji Kong, and Rendong Ying

Applied Mechanics and Materials, Volume 538, April 2014, Pages 289-292

PPMA: Parallel Programming Model for an Audio Application Specific Multi-core DSP

Xu Jiangwei, Wei Zhenqi, and Liu Peilin

2014 Sixth International Symposium on Parallel Architectures, Algorithms and Programming

Optimization of ETSI DSR frontend software on a high-efficient audio DSP

Zhenqi Wei, Peilin Liu, Cun Yu, Hongbin Zhou, Ying Ye, Ji Kong, and Rendong Ying

2013 IEEE International Symposium on Circuits and Systems

A Smart Format Floating-point Engine for GNSS Receiver

Hongbin Zhou, Rendong Ying, Peilin Liu

Proceeding of ION GNSS 2012

StreamPoP: Stream programming oriented power-efficient audio DSP

Ji Kong, Peilin Liu, Zhenqi Wei, Kun Yang, Ying Ye, and Rendong Ying

2011 IEEE International Symposium on Circuits and Systems

Low-power microarchitecture of zero-overhead nested loops in embedded processors

Zhenqi Wei, Peilin Liu, Ji Kong, and Rendong Ying

International Symposium on Intelligent Signal Processing and Communication Systems December 2010

Next-generation consumer audio application specific embedded processor

Ji Kong, Peilin Liu, Xianmin Chen, Jin Wang, Xingguang Pan, Jun Wang, He Xiao, Zhenqi Wei, and Rendong Ying

2010 IEEE 8th Symposium on Application Specific Processors

A novel reconfigurable scratchpad memory for audio applications on cost-effective SoC

Ji Kong, Peilin Liu

In VLSI System on Chip Conference (VLSI-SoC), 2010 18th IEEE/IFIP