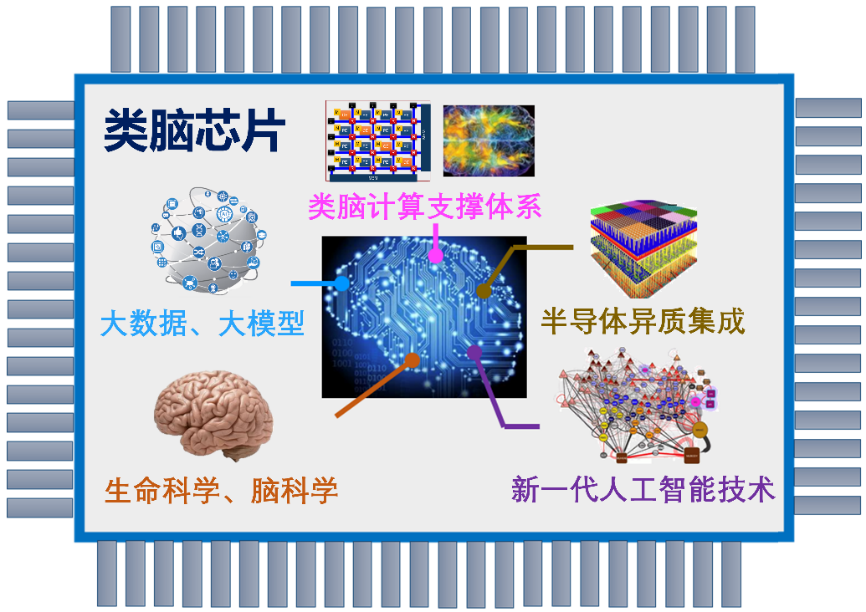

针对当前人工神经网络(Artificial Neural Networks, ANN)在功耗、运算量、泛化性等方面面临的瓶颈问题和发展局限,我们致力于面向下一代类脑神经网络,研究大规模脉冲神经网络(Spiking Neural Network, SNN)的高仿生建模、高效学习、高性能芯片架构,研制支持在线学习的类脑芯片,结合新一代人工智能技术及半导体技术的发展,实现高性能神经形态计算,构建类脑在线学习支撑体系及其应用生态,推动通用人工智能长远目标的实现。

类脑芯片宏观架构

1 类脑芯片架构

架构方面,我们的总体目标是设计面向在线学习的低功耗、可塑性事件型处理架构。具体地,针对边缘计算设备的多样性以及性能、场景对于类脑芯片架构的多元化需求,开展边缘场景的抽象化统一模型的研究,设计具有数据-指令融合的分布并行流驱动处理、事件触发计算、弹性多模态运算引擎、众核协同自适应功耗分配等特点的新型类脑计算芯片架构。

- 在计算核方面,研究基于弹性多模态计算引擎的可重构计算核心,兼容多种神经元模型状态更新和发放特性,突破固定计算核心所导致的计算能力局限性,实现灵活高效的神经元计算核心设计。

- 在片上网络路由器方面,研究低时延、低功耗片上互联的共享资源路由架构,为神经元的多模式信息传递需求提供有力保障。

- 在通信互联方面,研究类脑芯片架构的异步通信方式,适应类脑神经网络结构中的高效异步通信特点,满足高效异步通信的扩展需求。

- 在流驱动处理、事件触发计算方面,研究数据-指令融合的流驱动计算模型,适应类脑神经网络分区并行计算特性,满足大规模类脑神经网络的高效计算需求。

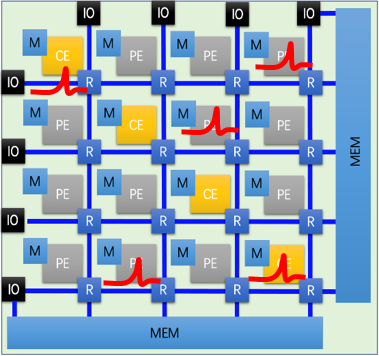

计算核-路由架构

目前实验室在这一方面开展的研究如下:

类脑通用计算核心

为提升计算核的计算速度,需设计固定结构计算核,实现针对特定算子的运算加速;另一方面,为提升计算核的通用计算能力,突破传统固有结构计算限制,又需设计可编程通用计算核,能够兼容多种神经元模型或自定义算子,实现可重构的计算核心,最终设计出可编程软核、固定结构加速核混合的众核架构。

计算核-路由架构

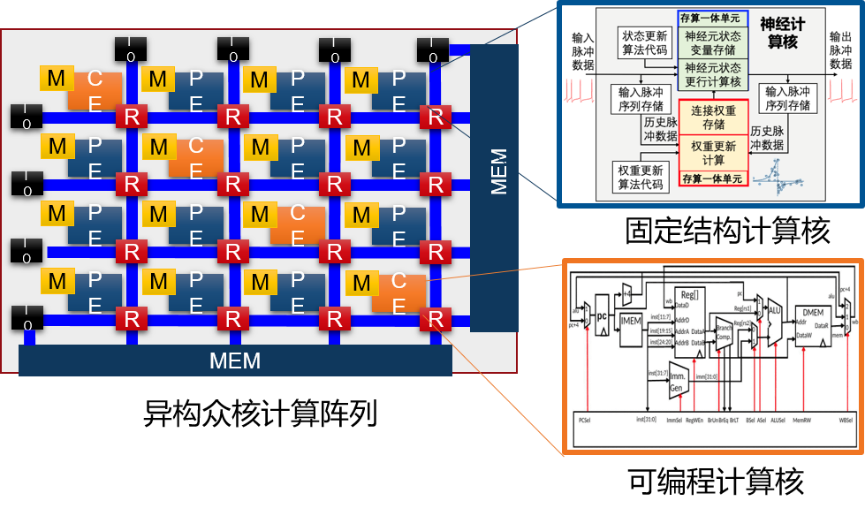

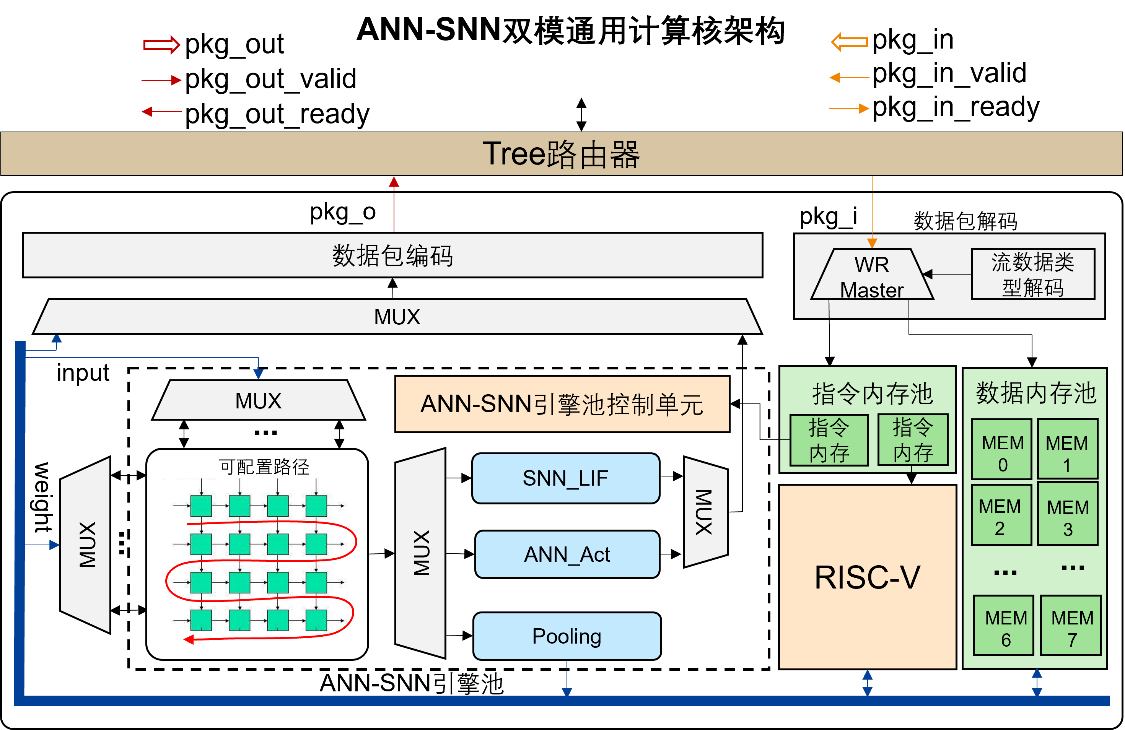

计算核方面,目前设计架构如下。通用计算引擎包含定制化加速硬核和软核。

- 定制化加速硬核为ANN-SNN计算引擎,可通过指令简单配置为ANN或SNN计算模式,仍保留了一定的通用能力;

- 软核为三级流水线的RISC-V处理器。

通用ANN-SNN硬核能够配置为执行SNN或ANN计算,对应参与计算的数据为特征图或者脉冲数据。除通用ANN-SNN硬核与RISC-V软核之外,通用计算引擎还包含用于数据包编解码的功能模块、指令内存池以及权重或激活数据内存池。

通用计算核架构

类脑众核路由架构

片上路由网络方面,实验室致力于研究高能效片上网络互联通信路由器架构。针对众核架构的需求。片上路由网络在支持数量庞大的异构计算核心的同时,需要在资源的限制下达到平衡。根据Mesh路由和Tree路由各自的优缺点,将两者相结合,设计出路由网络结构如下图所示,Mesh路由不直接和计算核心通信,而是作为数据传输通信的介质,将数据从来自不同方向的路由传向目的方向的路由,接入总线;Tree路由与四个计算核心相连,接收Mesh路由传来的数据,可以是权重、指令、脉冲等信息,并将数据信息传入对应的计算核心进行处理,处理后的数据再经由该Tree路由传入Mesh路由,进行后续的数据通信。与单独使用Mesh路由下一个路由只能与一个计算核心通信相比,混合结构下一个路由可以做到与四个计算核心通信,空间资源需求增加的情况下,计算效率得到更大的提升。

MEM

MEM

Tree路由

mesh路由

Mesh-Tree混合片上路由架构

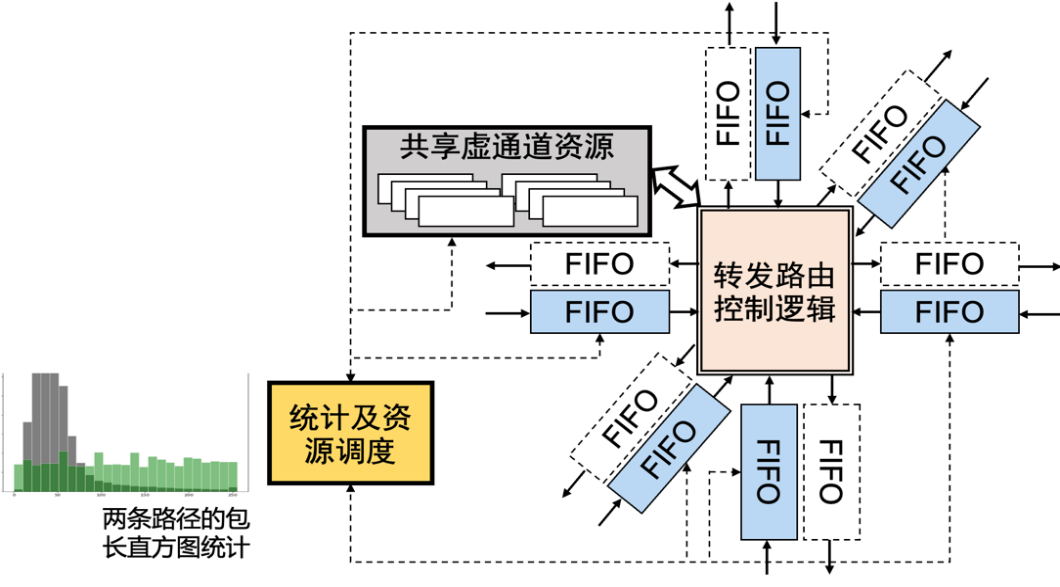

在Mesh-Tree混合结构的基础上,为更好地提升性能,针对单个路由器,实验室还提出高能效自适应优化片上路由器的概念。如下图所示,该路由器具有以下结构特点:

高能效自适应优化片上路由器

- 多通道端口:和传统路由4端口相比,我们的路由增加2个端口,最大支持6双向收发端口。在虚拟通道存在的情况下,单个路由传输数据量、复用率得到提高。

- 虚通道资源共享:引入共享虚通道模块,流入路由器的数据都可以被各个端口获取,为路由器各通道按需分配硬件资源,以较少的缓存空间满足脉冲神经网络输出脉冲的突发性和集中性特点打下基础。

- 在线调度监控技术:引入统计及资源调度模块,记录路由器不同端口的数据包流量,通过实现低复杂度通信统计量算法,为在线资源配置优化提供定量依据,支撑路由器的动态自适应资源分配。

- 全局功耗优化管理模块:基于神经网络功能分区的特点,根据功能区通信需求和能耗差异,在线计算映射方案,增量式地调整计算核布局,平衡计算量、能耗和通信带宽。

2 类脑芯片软件部署工具链

在软件部署方面,类脑芯片软件部署工具链实现应用模型到类脑芯片的配置、映射、调试、编译,并最终实现在类脑芯片上训练和推理。构建算法级、算子级和芯片行为级仿真平台,实现各个级别不同组件的协同仿真以及软硬件的相互验证,实现算法到芯片的联合优化,支撑自动化高效率的硬件架构评估和算法验证,保障类脑算法的高性能部署。

目前实验室在这一领域开展的研究如下:

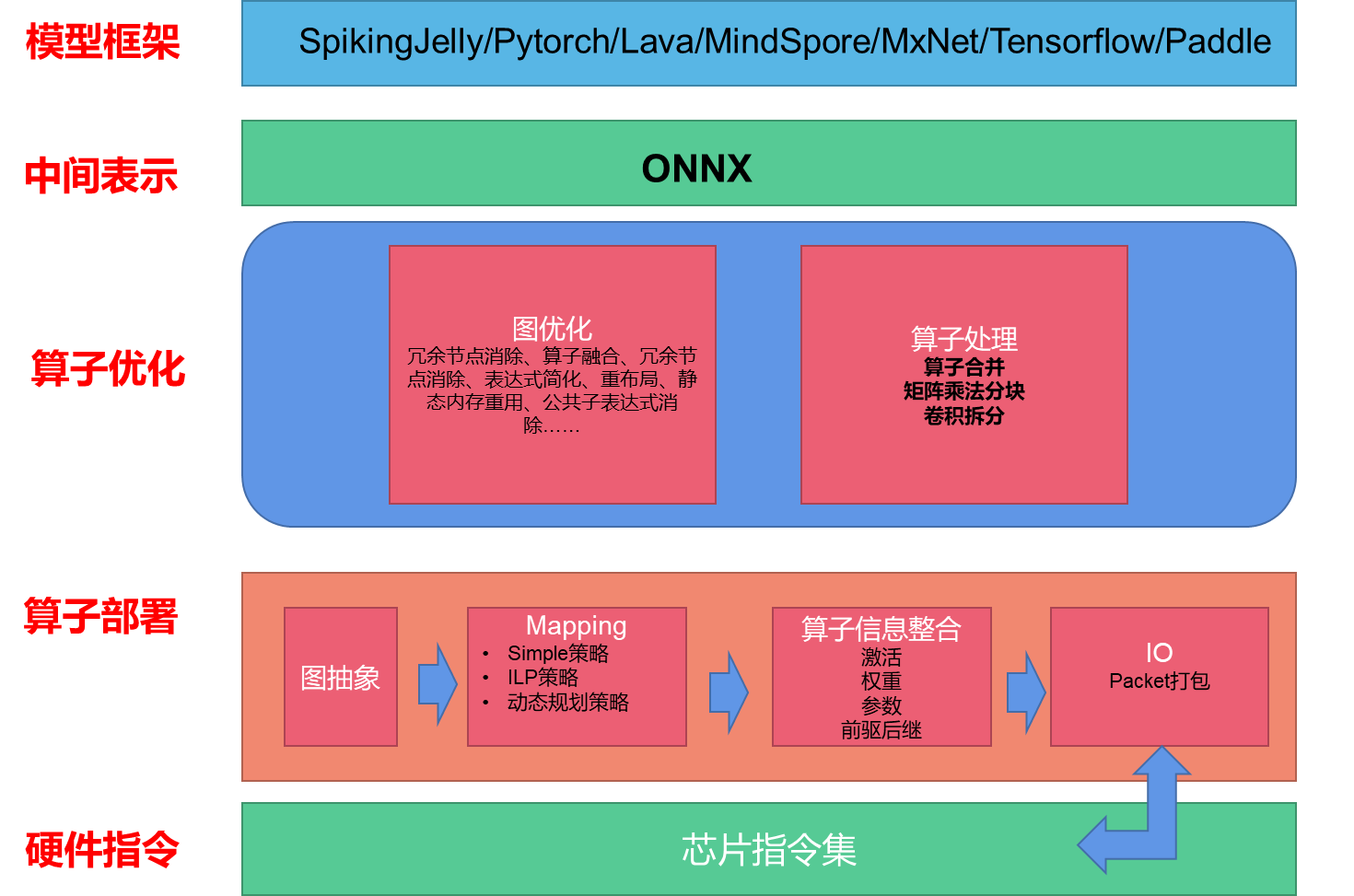

2.1 类脑芯片编译器

类脑芯片编译器是将高级编程语言编写的类脑应用模型转换成类脑芯片可识别的二进制指令的过程。本实验室研发了类脑芯片前端编译器。编译器的架构分为5层:

- 深度学习框架:对接各类深度学习框架

- 中间表示:计算图或算子,一般以ONNX表示。

- 算子优化:设备无关的计算图优化

- 算子部署:算子到众核物理单元的映射

- 机器指令:芯片硬件指令集

类脑编译器架构

2.2基于SpikingJelly的LIF算子转ONNX方法

将脉冲神经网络模型转为ONNX等中间表示(IR)是类脑芯片编译器关键的一步。类脑芯片设计有可编程计算核,支持专门的LIF,Hodgkin-Huxley,IF,IZH神经元加速的,但是ONNX里不支持单独的LIF等算子。目前,Loihi、Tianjic等类脑芯片配套的编译器均是自研专用,通过将SNN神经元算子以JSON格式表示,由硬件直接读取JSON配置文件处理,跳过了中间表示(IR)这一步骤。由于未采用IR,其模型失去了通用性,无法在其他硬件平台执行。为了解决这一问题,本实验室以SpikingJelly框架为例,研究了将LIF算子转换为ONNX的两类方法:拆分法,转换后的模型中LIF神经元的行为被拆分成了加法、除法等基础算子;自定义算子法,将LIF神经元的行为整合到单个算子中,通过定义symbolic方法可以将该算子转换到onnx模型。本套工具可以适配TVM等主流深度学习编译器,为SNN模型的跨平台部署提供支持。

设置前向/反向传播替代函数

导出中间表示

拆分SNN运算

拆分法过程

自定义算子

注册算子

导出中间表示

自定义算子法过程

2.3计算图到众核映射工具

Mapping是将计算图(上面得到的)映射到众核处理器的过程。实际上是一个graph到众核的映射过程。本实验室提供3个mapping方法:Simple方法、整数线性规划方法、动态规划方法。

- Simple策略

顺序遍历算子,以此放在第1个计算核、第2个计算核……、第n个计算核。当计算核数量不够时,重新从第1个计算核开始分配,即:第n+1个算子分配到第1个计算核,第n+2个算子分到第2个计算核,……,以此类推。

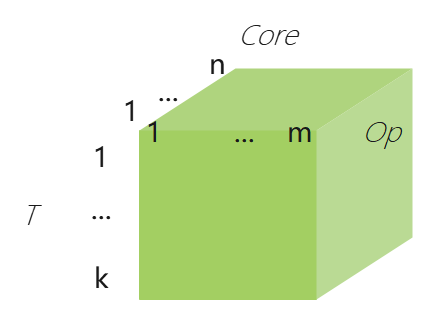

- 整数线性规划法(ILP)

对于众核芯片的算子映射问题,本质是是同时存在时间和资源约束的调度问题,因此可以建模为线性整数规划法。线性整数规划法将调度问题表达为一组满足不等式约束的线性目标函数。如下图所示,有m个算子(Op),n个计算核(Core),T个时间步(T)。定义决策变量x_ijk,x_ijk=1表示算子i被部署到计算核j的第k个时间步。其约束条件包括算子约束、资源约束、顺序约束。优化目标为最小化核间通信跳数。

ILP方法建模示意

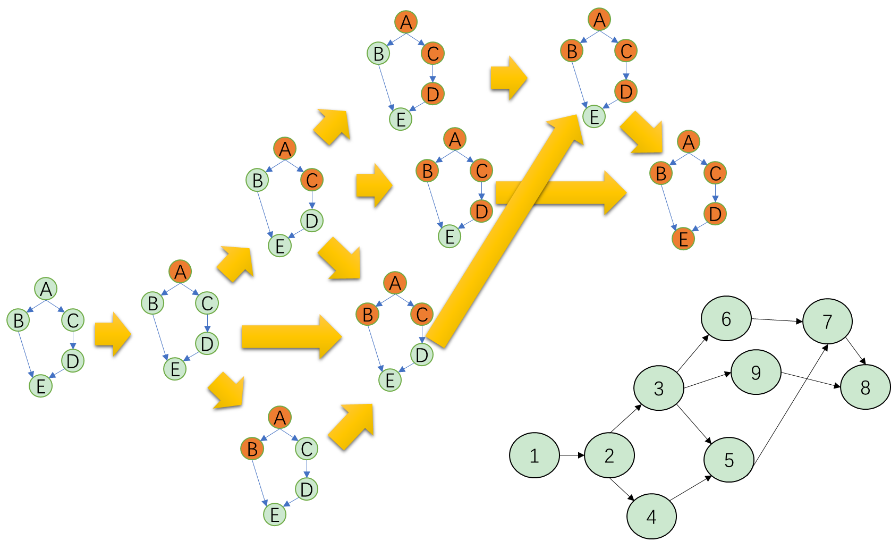

- 动态规划法

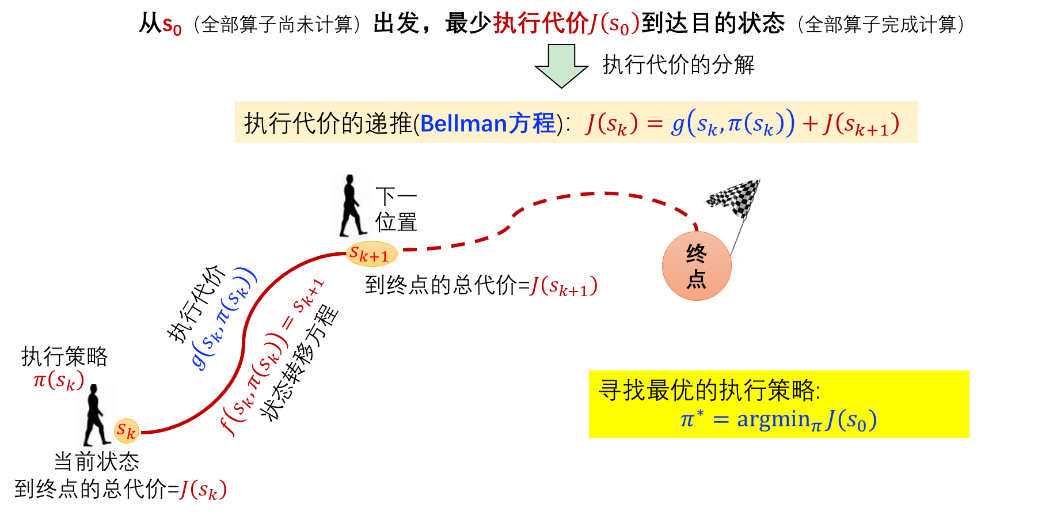

动态规划法把状态定义为当前完成的算子组合,动作定义为基于当前状态,下一个能够执行的算子的集合,执行代价定义为运算时间、执行能耗、通信代价、缓存代价等,终止状态对应所有算子被执行完成。复杂度的扩展包括并行计算条件下的状态图、任务分配、时间不同步等。通过建立执行代价的Bellman方程,可以寻找最优的执行策略。

动态规划法示意

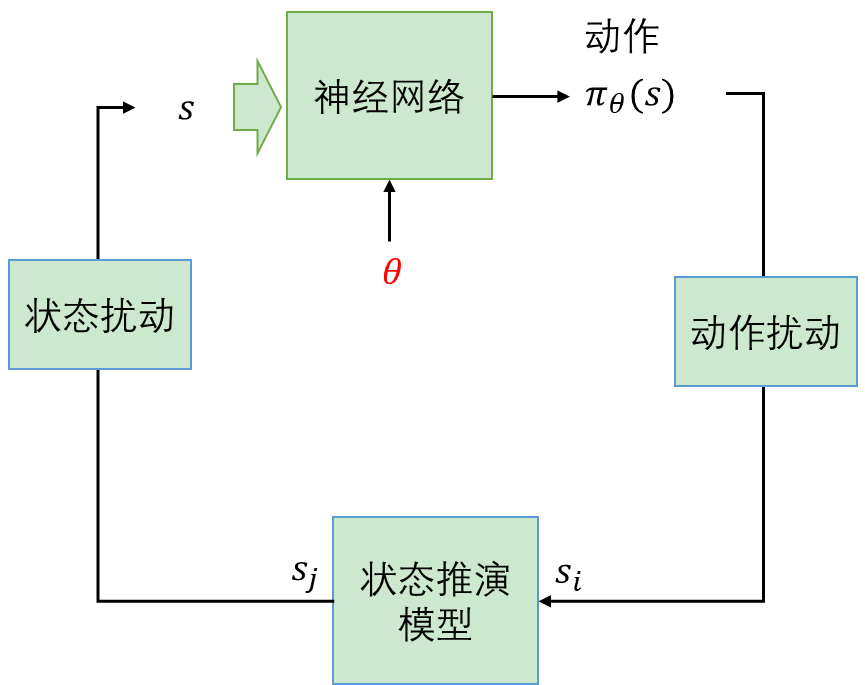

基于ADP的计算度调度和分配

3类脑视觉计算架构

以深度卷积神经网络(DCNNs)为代表的计算机视觉或机器视觉在许多视觉任务中取得了巨大成功。 DCNNs通过模拟生物视觉腹侧通路的前馈和分层结构,在图像分类等任务中取得了极高的准确性。然而ANN取得的成就基本上都是以高昂的功耗、计算以及数据成本为基础。近年来,受生物大脑计算原语启发的神经形态计算在连续数据流处理上的可伸缩性、低功耗等方面具有极大的潜在优势,有望解决目前计算机视觉的高功耗、复杂计算量、低泛化性等问题。

类脑视觉,即所谓的大脑启发的计算机视觉,仍然是加快计算机视觉发展的一种有前途和有效的方式。生物启发的计算机视觉旨在学习生物视觉系统以开发先进的图像处理技术,我们致力于基于SNN和生物视觉机理实现高能效类脑视觉处理架构,以解决目前计算机视觉面临的复杂度、能效等瓶颈问题。

3.1 3D图像处理器

- 3D 深度图像处理技术

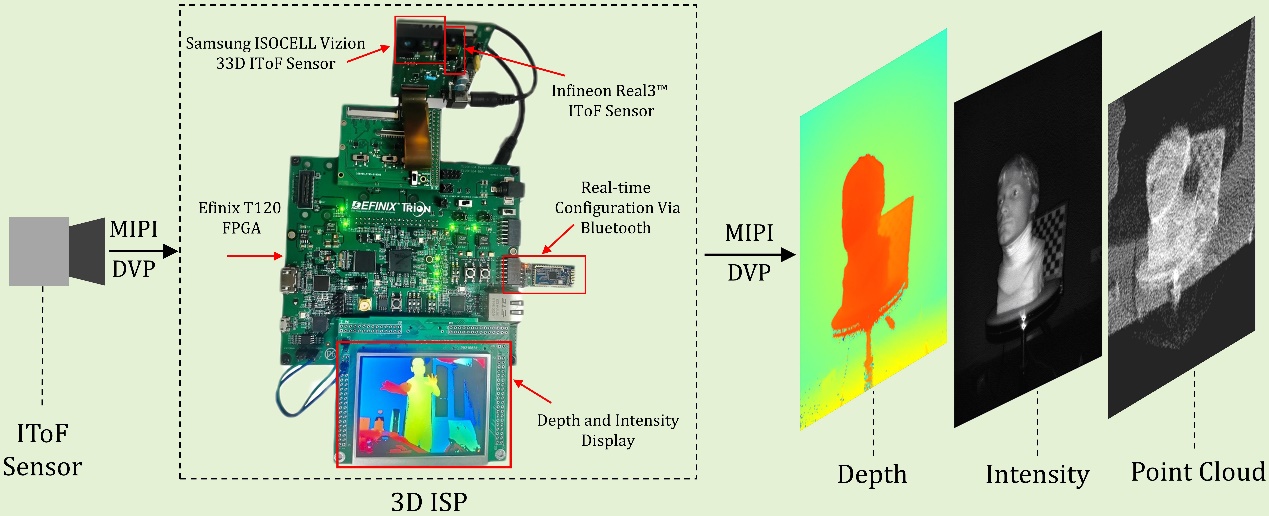

深度图像是指将从图像采集器到场景中各点的距离(深度)作为像素值的图像,它直接反映了景物可见表面的几何形状。我们研究了一种通用的3D图像信号处理器(ISP)以解决3D飞行时间(Time of Flight)传感器的Raw域和深度域图像处理问题,兼具有高实时性和高能效。

我们提出的3D ISP提出了:

- 可配置的缓存策略,以提高非流式存储器访问的效率,并支持不同的IToF传感器。

- 为了解决IToF传感器中普遍存在的相位模糊问题,开发了一种硬件优化的级联多频率融合方法,该方法不仅支持多达6个调制频率,而且有助于多路径干扰的逐像素检测。

- 提出了用于深度计算和校准3D图像增强和后处理的可扩展计算引擎。

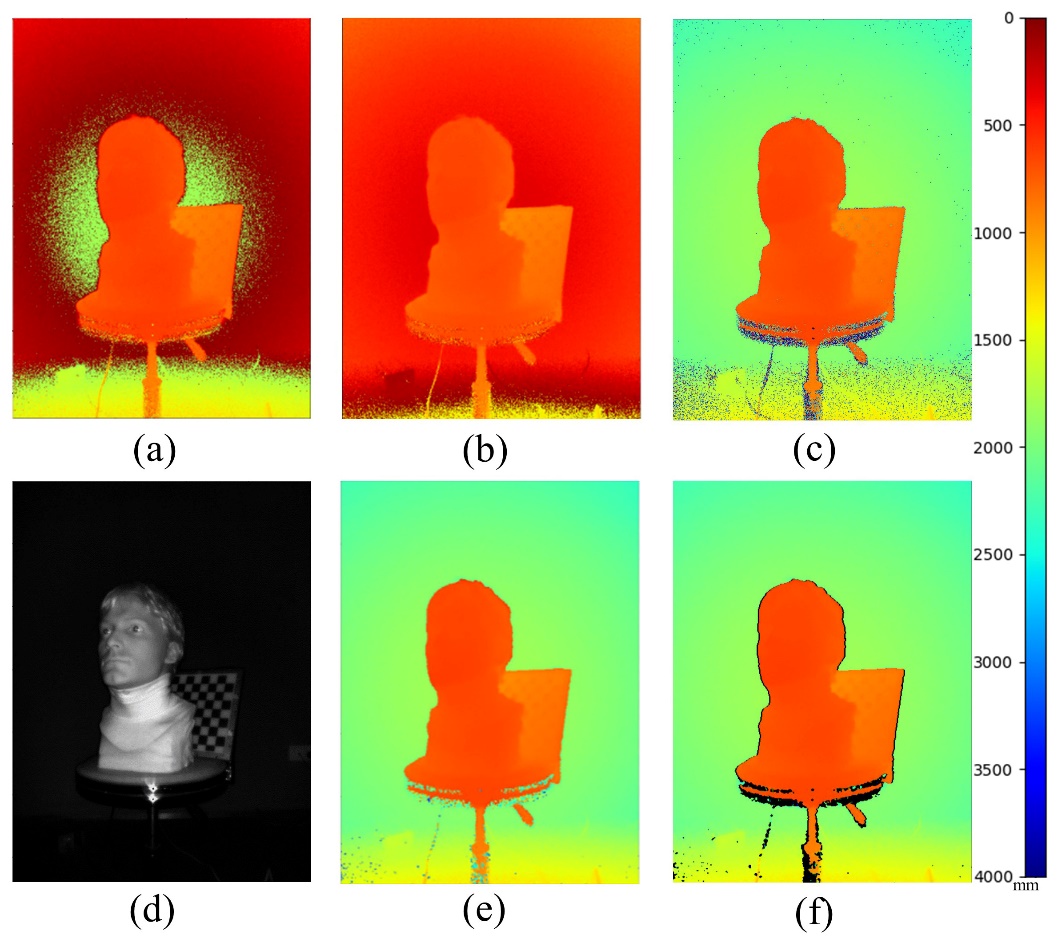

结果表明,3D ISP具有可忽略的精度损失和低延迟,与Intel CPU上的实现相比,其能效提高了53.35倍,比ARM CPU实现提高了55.45倍。当以75MHz运行时,3D ISP可以支持1280×960深度、强度和点云输出,帧速率为30f/s。下面是该工作的一些原型展示和多频合成实验结果。

3D ISP流水线概览

3D-ISP原型FPGA芯片

深度图像处理结果(单频-多频)

- 3D 点云图像处理技术

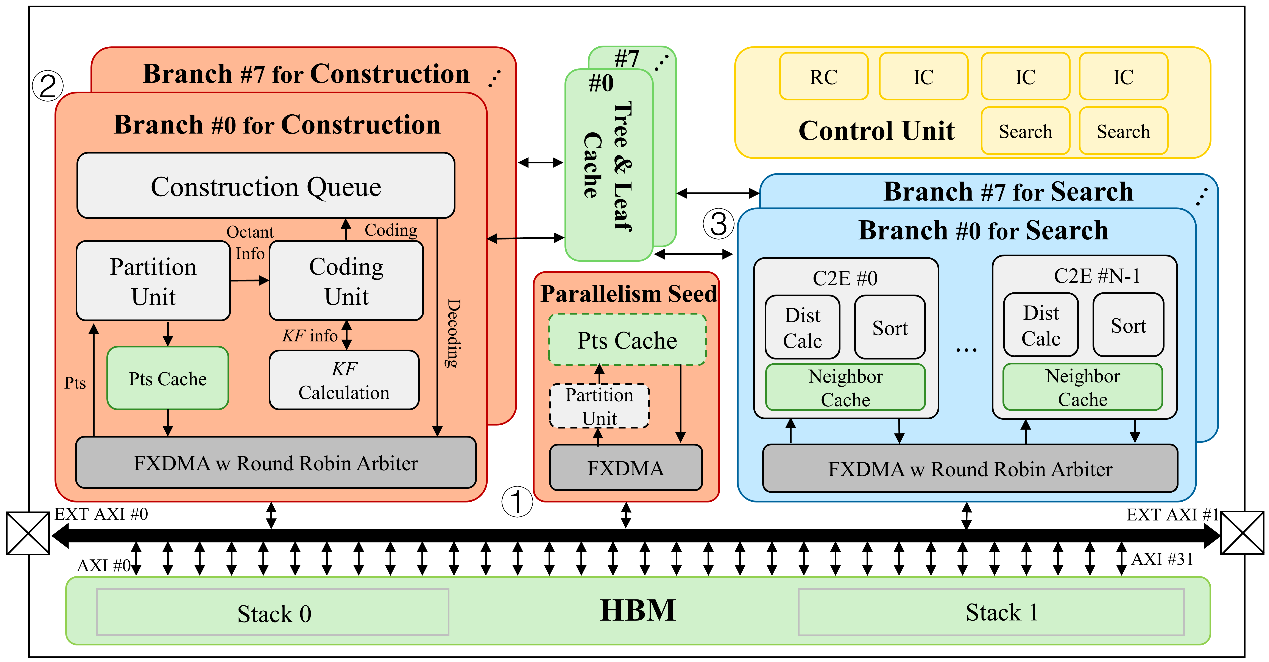

随着光探测和测距(LiDAR)逐渐成为机器人导航和自动驾驶中的一个重要组成部分,需要实时处理高吞吐量的3D点云。我们研究了3D点云处理核—k近邻(kNN)搜索,提出了一种高度并行的架构,即ParallelNN,用于高吞吐量点云的高效kNN搜索处理,贡献如下:

- 优化了基于高带宽存储器(HBM)和片上存储器的多通道缓存,以提供大的外部带宽。

- 提出了一种新的并行深度优先八叉树构造算法,并将其映射到具有跟踪编码构造队列的多个构造分支上,该算法可以规则化随机访问并高效地执行多分支八叉树的构造。

- 提出了算法架构协同优化,包括基于并行关键帧的调度和多分支灵活搜索引擎,以提供参考点的无冲突访问和最大重用机会,与基线架构相比,实现了27.0倍以上的加速。

我们在Virtex HBM FPGA上原型化ParallelNN,并在KITTI数据集上执行广泛的基准测试。结果表明,ParallelNN实现了比CPU和GPU实现高达107.7倍和12.1倍的加速,同时更节能,例如,分别比CPU和CPU实现高73.6倍和31.1倍。此外,通过所提出的算法架构协同优化,ParallelNN比最先进的架构实现了11.4倍的加速。下面是该工作的架构展示。

点云kNN处理架构

3.2 基于DVS的类脑目标检测架构

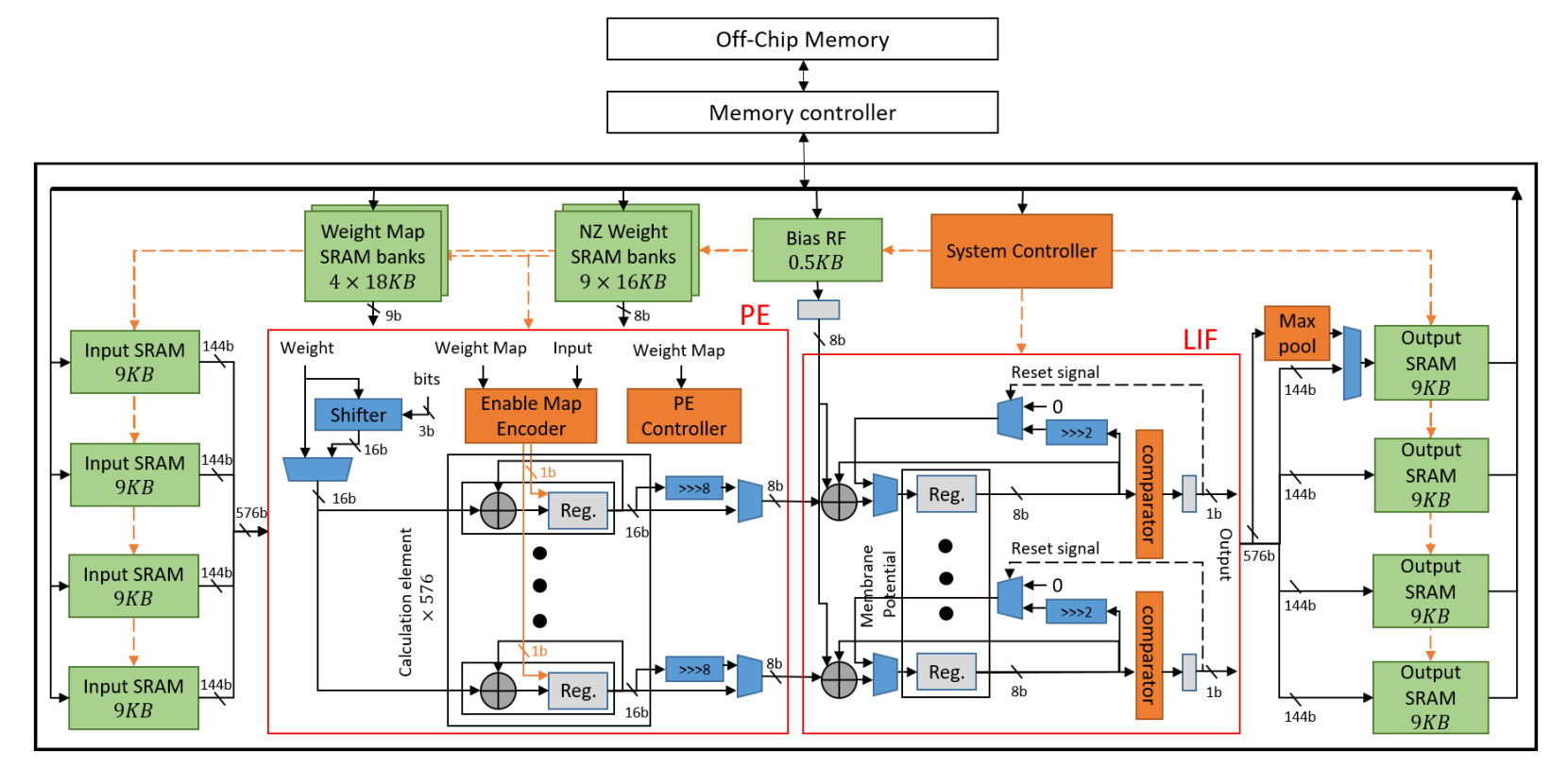

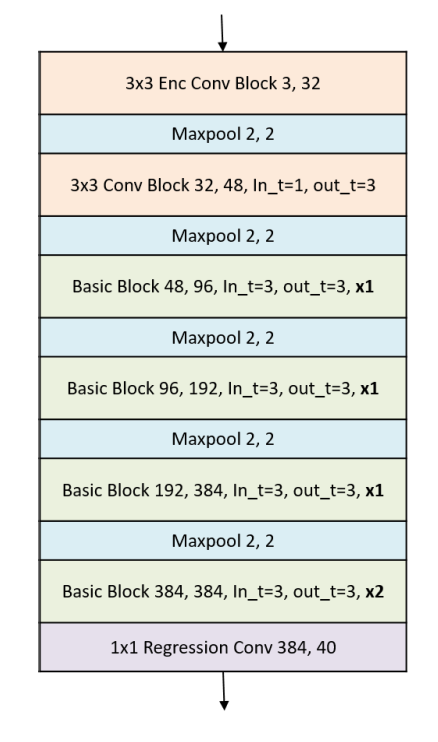

除了3D传感器研究外,神经形态传感器如DVS事件相机也是我们在类脑视觉领域研究的重点,原因之一就是DVS相机感知帧之间的强度变化,以稀疏事件流的形式感知环境,相较于传统RGB相机,拥有低功耗、高动态、高“帧率”的优势。同时在计算机视觉众技术领域中,目标检测作为图像分割、物体追踪、关键点检测的前提,也是一项非常关键而基础的任务。我们基于SNN研究了稀疏计算加速器用于高能效目标检测,该设计具有以下特点:

- 在具备天然稀疏性的脉冲神经网络中利用细粒度剪枝技术使网络更加稀疏;

- 基于脉冲神经网络的时间相关性提出了一种混合时间步长的方法以减少操作次数并更加精确的提取图像特征;

- 采用位掩码技术对稀疏权重进行压缩存储,并采用零激活门控跳零技术降低延迟,降低PE动态功率。

整体SNN目标检测加速器架构

混合时间步长卷积框架